今年8月,The Information爆料了苹果和台积电之间的“甜心交易”(sweetheart deal):苹果下单了台积电3nm工艺,但台积电必须独自承受报废芯片的良率损失,这一举措能为苹果省下几十亿美元的成本[1]。

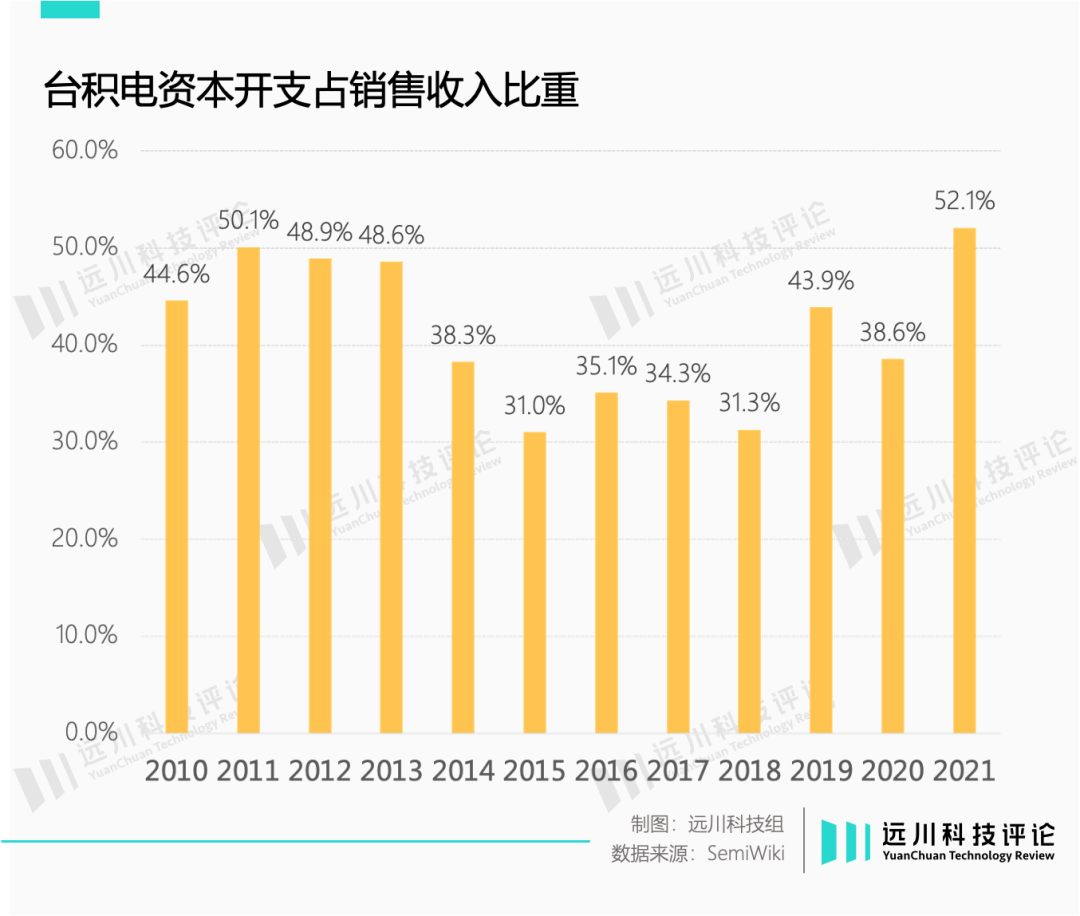

曾经苹果和台积电被称为“最完美的合作关系”:借由安芯网规模庞大的研发投入和资本开支,台积电在芯片制造上始终保持领先,苹果则用大规模的订单给台积电报销开发成本,帮助其进一步扩大领先优势。

然而,这个双赢合作却在这两年出了些问题。

一方面,电子元件商城先进制程的开发成本越来越高,台积电也有点扛不住。另一方面,由于手机市场的萎靡,最爽快的两大客户苹果和高通也难免囊中羞涩。

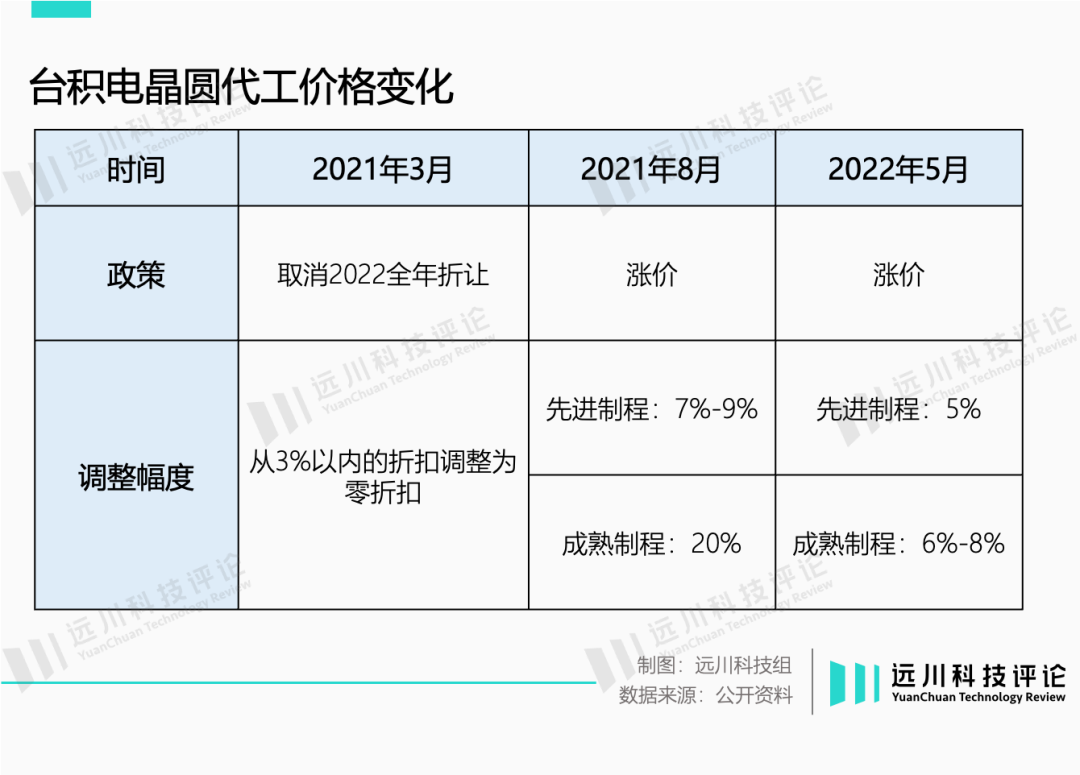

面对巨大的利润压力,台积电选择先涨为敬。根据媒体报道进行估算,2023年台积电的晶圆代工价格与两年前相比大约上涨了16%(先进制程)到34%(成熟制程)。在过去十多年里,台积电都从未大幅提价。

在台积电宣布涨价后,苹果曾以一贯的强势态度表示坚定拒绝[2],几经博弈之下,才有了那份“按良率付费”的协议。

去年10月,台积电还颇有先见之明的表示,预计2023年整个半导体行业可能会下滑,于是下调资本开支至360亿美元。

结果两个月后ChatGPT横空出世,全世界的AI芯片公司又把台积电送上了神坛。

昂贵的进步

今年9月苹果发布会结束,顶着“首个3nm制程芯片”的A17 pro问世,10%的CPU性能提升让人忍不住感叹牙膏还能这么挤。台媒第一时间出来为台积电甩锅,表示主因在于苹果的设计过于保守,加上iPhone散热效率太差,影响了3nm制程的发挥。

为了3nm工艺节点,台积电不可为不尽力,创下历史新高的资本开支就是最好的证明。

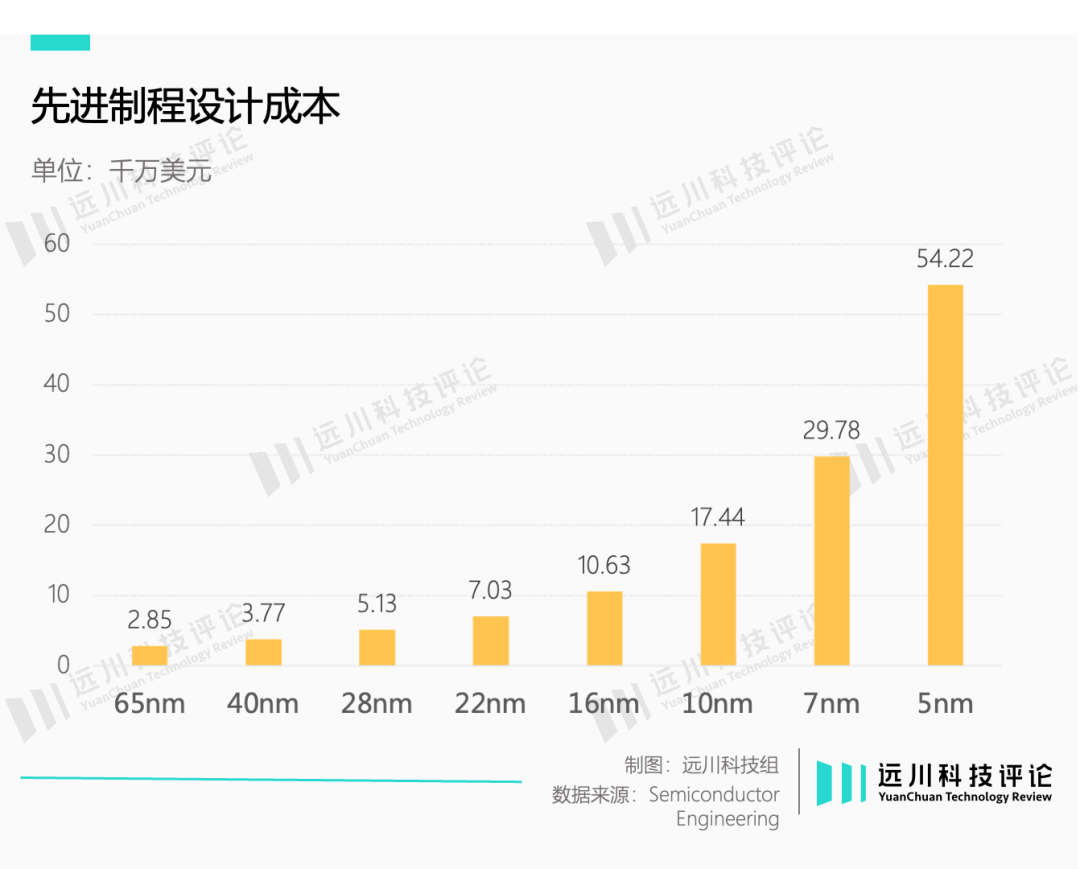

一般来说,电子元件采购芯片制程越先进,需要的生产环节也就越多,成本自然水涨船高。在一些特殊节点,由于生产工艺的彻底改变,原本的设备和产线会被彻底淘汰,成本瞬间被拉高。

所谓刻蚀,就是将光刻标记出来的区域,通过物理或化学方法去除,精准雕刻出设计好的功能外形。由于光刻技术受波长限制,单凭光刻机很难满足5nm、3nm及更先进的工艺,只能通过反复的刻蚀来实现更小的尺寸。

现阶段先进制程工艺的提升,相当程度上源于刻蚀步骤的叠加。因此近两年刻蚀和薄膜沉积(刻蚀的逆过程)在设备行业的市场份额极速上升,甚至超越了光刻机。

后者则创造了14/16nm这个经典制程:在14/16nm之前,芯片制造的主流工艺是HKMG(High-k Metal Gate),2014年,三星依靠梁孟松团队抢先台积电攻克14nm。当时,梁孟松用了FinFET工艺解决了生产问题,但工艺变化也意味着设备、产线的大手术。

一些晶圆厂在14nm的生产良率反而超过28nm,也是工艺变化的原因。

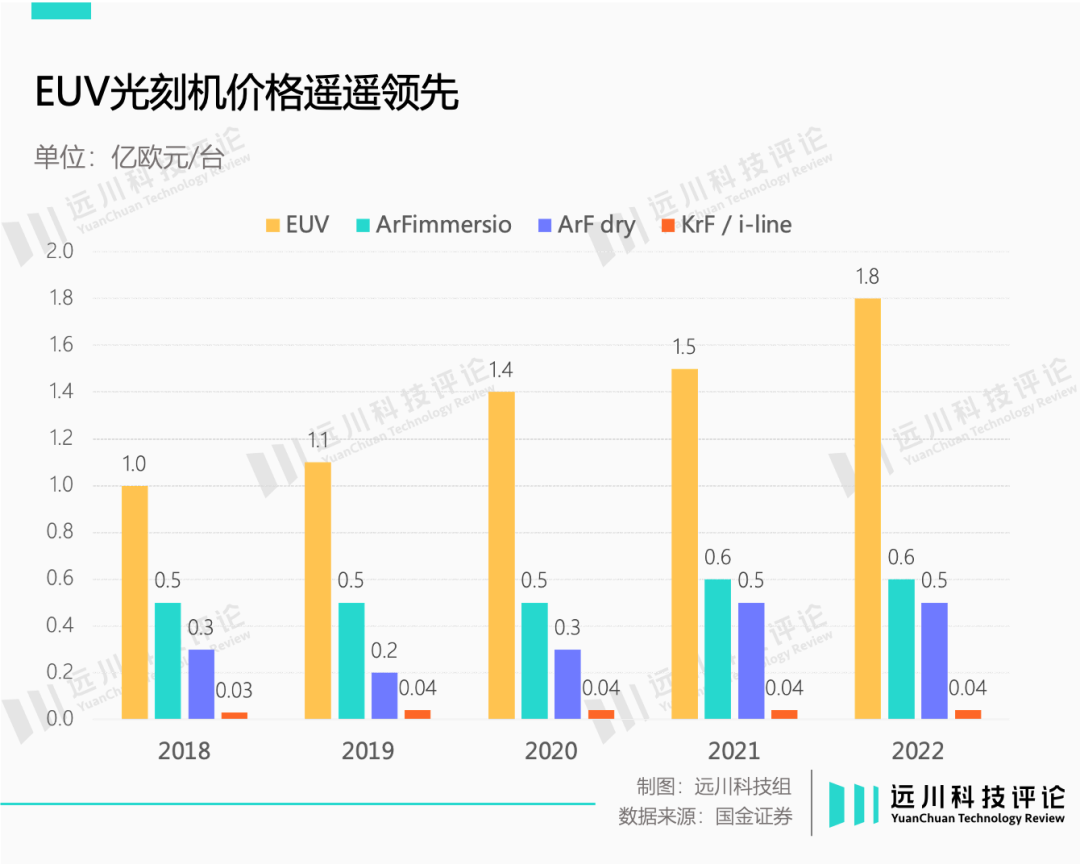

而由于DUV光刻机的精度限制,芯片制造深入到7nm制程后,就需要用EUV光刻机,价格是DUV光刻机的至少3倍。[3]台积电曾尝试利用DUV光刻机+多重曝光的方式生产7nm芯片,但扛不住低良率的巨额成本,最后还是老老实实买EUV光刻机。

这个昂贵的技术爬坡之所以多年来行之有效,是因为以苹果为首的一大批芯片设计公司,每年会排着队给台积电下订单。但当财大气粗的苹果都嫌贵的时候,这个循环就会出现问题。

根据IBS的测算,10nm,7nm和5nm芯片的IC设计成本分别1.7亿、3.0亿和5.4亿美元,而3nm芯片的设计成本则达到惊人的5亿至15亿美元。

由于芯片架构和IP复用等因素影响,业界对芯片设计成本的测算常常被高估。但即便排除这些影响,这也是个天文数字。任何芯片设计公司下单之前都得掂量掂量,自己有没有那么大的出货量。

越来越贵的成本只是台积电的焦虑之一。过去几年,台积电面临的问题有两个:

一是先进制程的高成本,导致钱砸的越来越多客户反而越来越少。

二是几个耗资巨大的工艺节点,产能高峰也就一两年,难以持续造血。

前者在业内被反复提及,后者则常常被忽略。

7nm:既不先进,也不落后

2019年,台积电痛失大客户华为,结果苹果、AMD这些大客户立马承包了闲置的产能,所以台积电一边说“影响不大”,一边宣布2021年起,台湾地区工作的5万名员工的通通涨薪20%。

由于众所周知的原因,7nm的热度在今年又被炒了起来。不过在台积电,7nm制程的处境一度尴尬。

台积电的7nm工艺创造了很多经典产品,比如苹果的A12芯片,AMD的Zen 2/3架构处理器,以及海思的麒麟985芯片。

一般来说,当一个新制程量产后,苹果和高通是第一个吃螃蟹的。而随着工艺升级,苹果和高通、AMD会更新到下一代制程,上一代制程的产能会降价,留给AMD等芯片公司。随着制程继续升级,成熟制程就会慢慢留给服务器芯片、汽车芯片等等产品代工电子物料。

对台积电来说,老制程虽然已经落后了,但产能不会被浪费。随着产线的成本慢慢折旧完,持续开动的产线反而能贡献可观的利润。在台积电的营收里,将近1/3都是40/45nm以上的成熟制程贡献的。